XIO2001 - PCIe Refclk recommended termination scheme for this clock when used in a Compact PCIe chassis? - Interface forum - Interface - TI E2E support forums

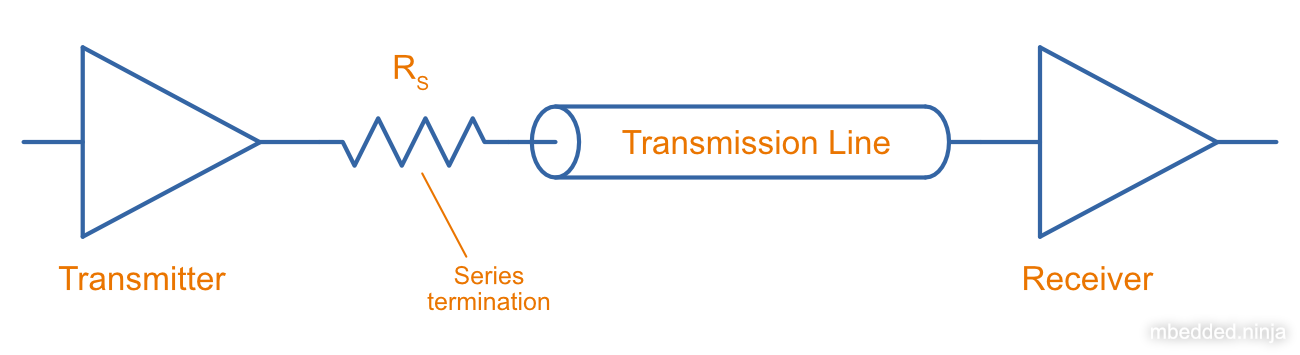

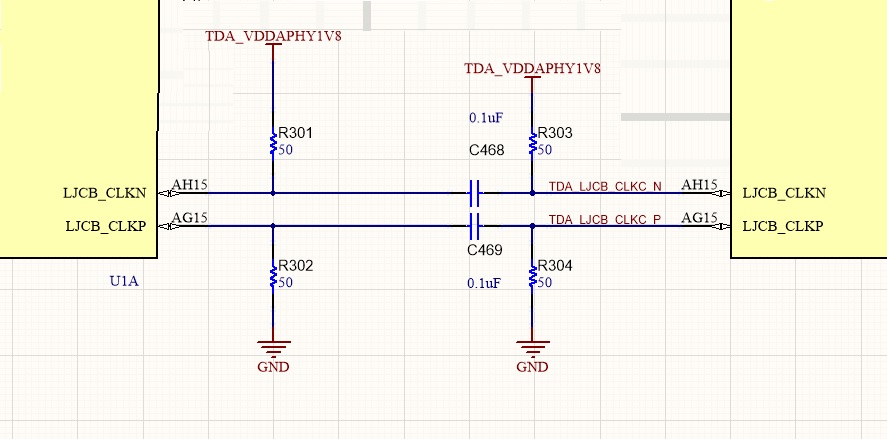

TDA2: Termination Resistors on PCI-e TX and RX - Processors forum - Processors - TI E2E support forums

TDA2: Termination Resistors on PCI-e TX and RX - Processors forum - Processors - TI E2E support forums

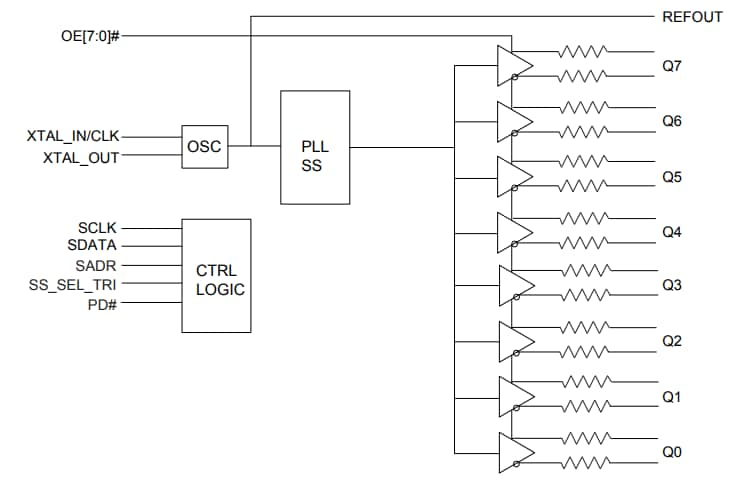

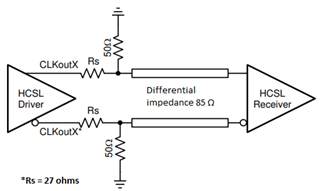

LMK00334: how to terminate 50Ohm at HCSL operation, DC coupling - Clock & timing forum - Clock & timing - TI E2E support forums

LMK00334: how to terminate 50Ohm at HCSL operation, DC coupling - Clock & timing forum - Clock & timing - TI E2E support forums

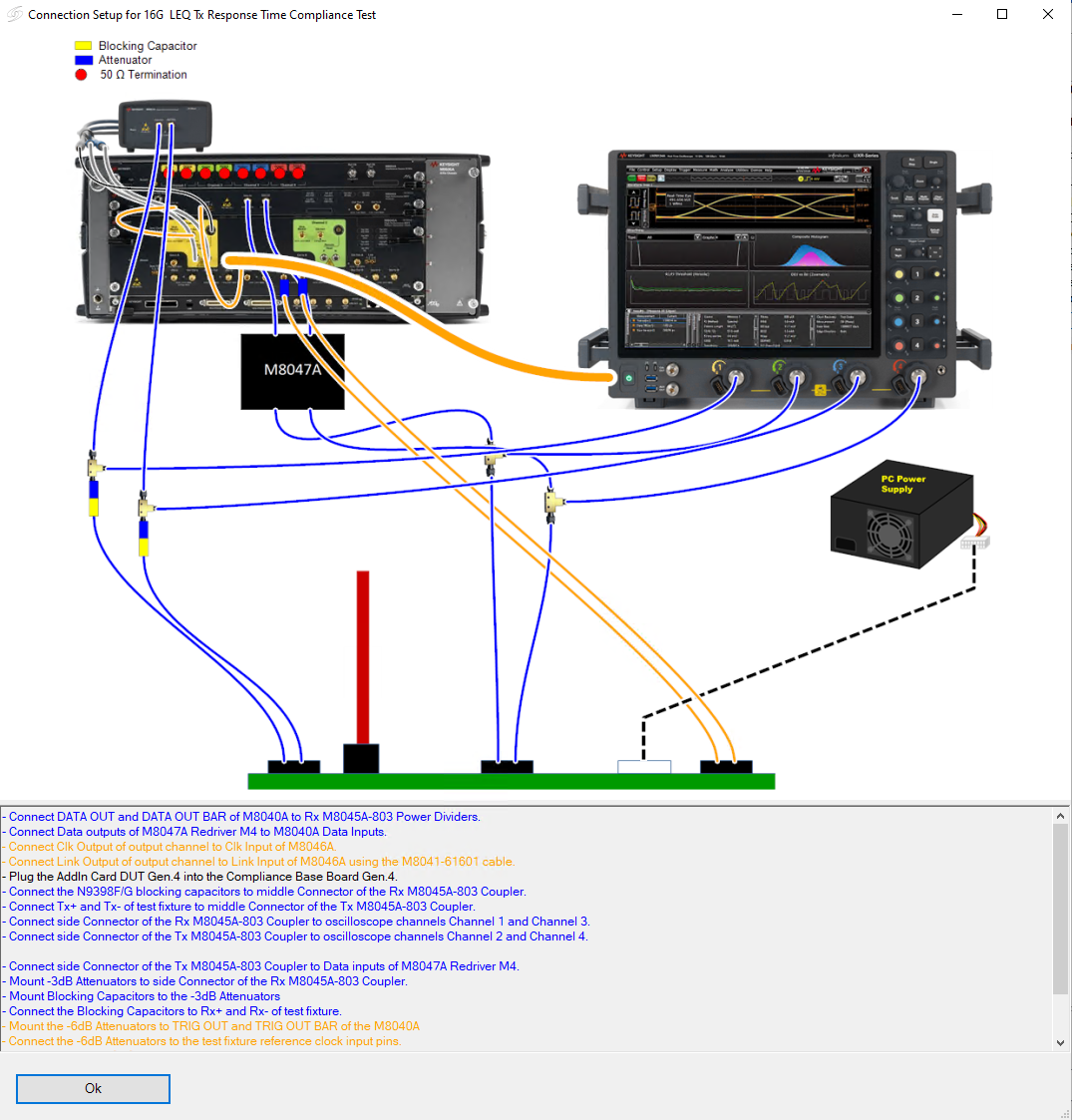

![C6655, PCIe] Is block diagram available for PCIe internal termination logic ? - Processors forum - Processors - TI E2E support forums C6655, PCIe] Is block diagram available for PCIe internal termination logic ? - Processors forum - Processors - TI E2E support forums](https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/termination_5F00_block_5F00_diagram.png)

C6655, PCIe] Is block diagram available for PCIe internal termination logic ? - Processors forum - Processors - TI E2E support forums

signal integrity - Why does FPGA PCI Express Tx output have on-chip termination of 100 Ohm? - Electrical Engineering Stack Exchange

![Electrical Physical Layer State in Power States - PCI Express System Architecture [Book] Electrical Physical Layer State in Power States - PCI Express System Architecture [Book]](https://www.oreilly.com/api/v2/epubs/0321156307/files/0321156307_ch12lev1sec9_image02.jpeg)